中国企业国际化发展 财务创新全球化研究 商务创新与全球化 境外直接投资备案(ODI) 国际风险管理 网络安全与隐私保护 泛珠三角区域合作 转创全球科创智库 管理创新与全球化 海关监管

电子商务师 知识产权发展 价值共创 企业科创管理 创投俱乐部 全面质量管理 移动支付 私营经济 企业经营 商业模式创新 通商董事会馆 灯塔工厂 企业产品创新 客户与营销 商业规划 产品检测 金融科技 价值网络 企业创新管理 科技创新企业 精益创新 玩具产业孵化基地 餐饮美食 奶茶饮品

十四五规划专题 碳达峰中和计划 科技创新 现代服务业 全过程工程 环保技术 跨境电商合规转型 数字化转型 碳排放管理 供给侧改革 转创国际技术转移 数控工厂 专精特新企业 能源与电力 碳排放管理会计 全面绩效管理 应对气候变化 国有资产管理 制度智库 雏鹰企业 高新技术企业 进出口企业管理 盈利模式转型 瞪羚企业 绿色能源与碳核算 气候审计与鉴证 数字化监管

电力系统自动化设备配置时钟同步系统,为不同的设备提供了时钟同步所需的时钟源。自动化设备多采用分布式系统架构,设备内模块之间也要进行时钟同步。自动化设备和模块的时钟同步,便于进行信息综合[1];同时,只有采用时钟同步手段,才能满足事件顺序记录(sequence of event,SOE)时标误差不大于1 ms的要求[2-3]。尤其在系统发生故障时,SOE时标的统一、准确,有利于事故原因分析。

时钟同步装置接收北斗/GPS卫星发送的授时信号,处理后向自动化设备提供时钟同步信号。时钟同步装置输出同步信号的方式主要有IRIG-B、IEEE 1588、秒脉冲(pulse per second,PPS)、分脉冲(pulse per minute,PPM)、简单网络时间协议(simple network time protocol,SNTP)、IEC 103报文等[4]。

本文主要研究了分布式系统内的串行通信对时设计。文献[5]介绍了一种采用串口对时和脉冲对时结合的方式。串口报文连接线负责设备日历时间的对时。PPS连接线下发同步信息。文献[6]介绍了一种采用串口分时复用的方式。串口连接线先下发日历时间,在整秒时刻再下发PPS同步码。以上两种方法均能实现较精确的对时。但方法一串口和脉冲对时线分开,受限于布线数目;方法二在中断中响应整秒同步码,中断响应延时不确定,影响对时精度和总线复用。本文设计的方案弥补了上述两种方法的缺陷。

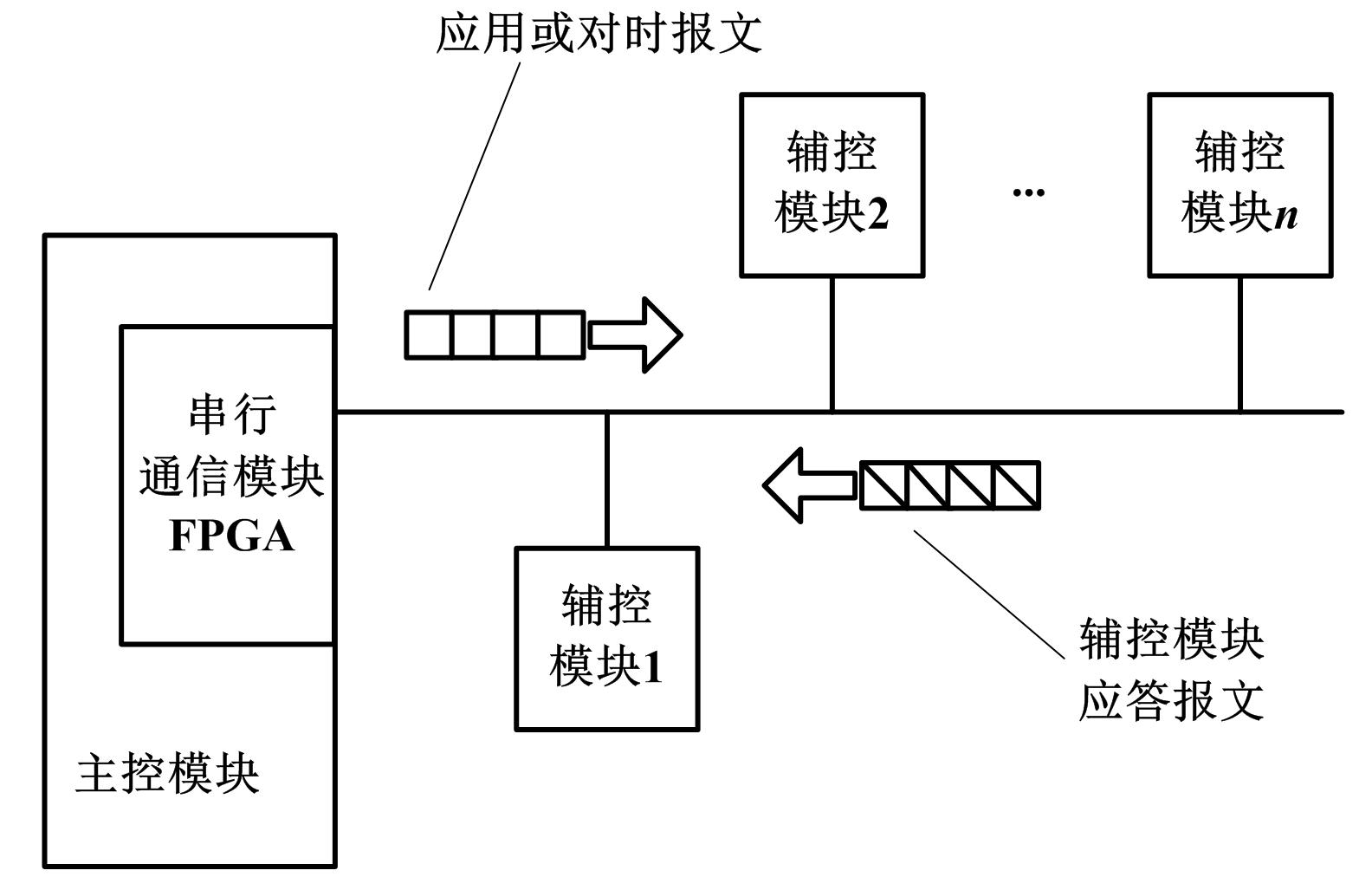

系统包含主控模块、高速串行通信总线以及挂接在高速串行通信总线上的辅控模块。主控模块借助现场可编程门阵列(field programmable gate array,FPGA)实现串行通信,在高速串行通信总线上传输数据通信和对时报文。数据通信报文采用主从轮询方式,辅控模块接收到该报文后回复报文;对时报文采用广播方式,辅控模块接收到该报文后只进行对时处理流程,不回复报文。

本文设计的分布式系统结构如图1所示。

图1 分布式系统结构图

Fig.1 Structure of the distributed system

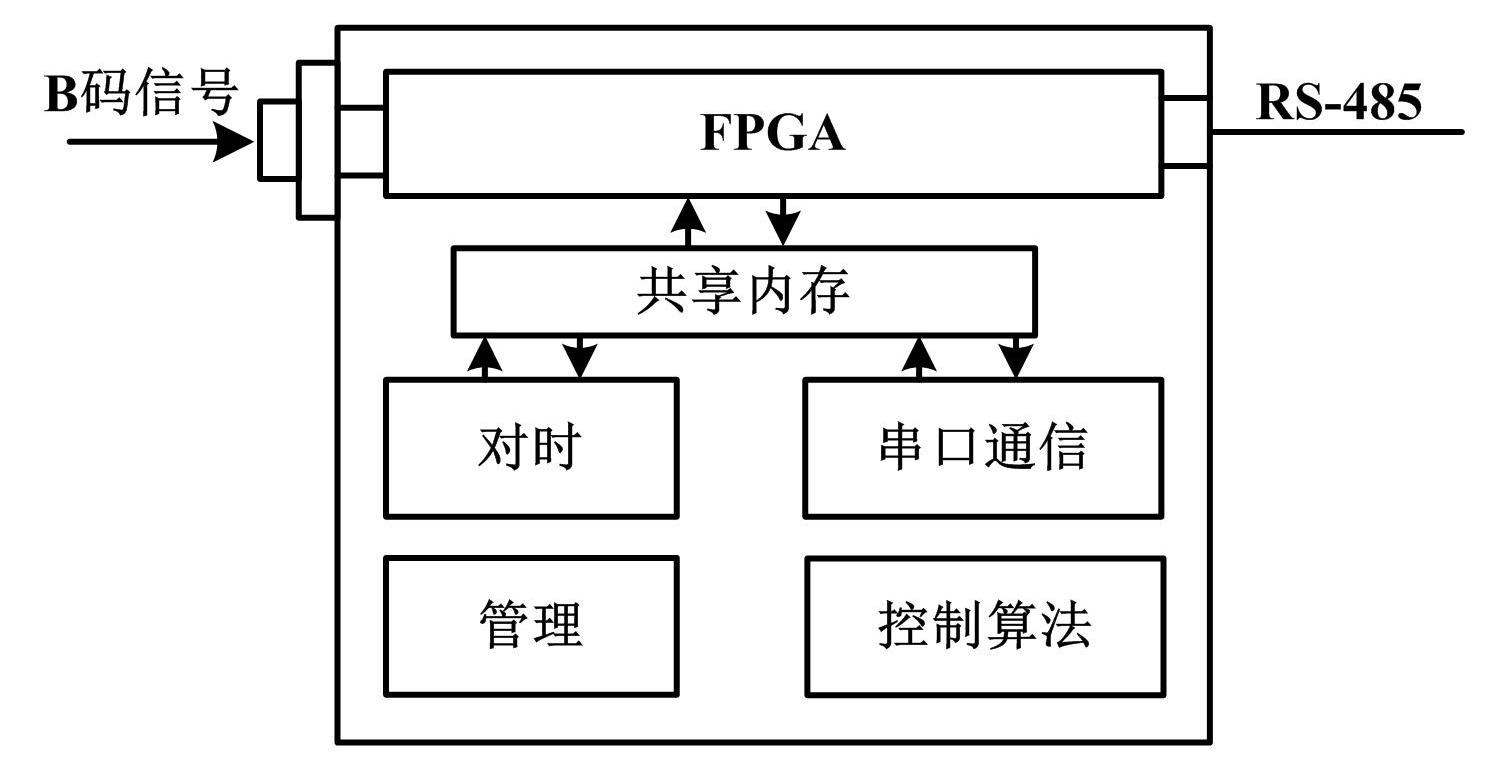

主控模块软件划分为管理、控制算法、对时、串行通信等模块。本文仅阐述与对时相关的内容。主控模块内部通过共享内存的方式进行数据交换。共享内存分为循环报文缓存区和管理内存区。

一方面,主控模块集成的FPGA通过IRIG-B方式从北斗/GPS授时装置接收授时信息,并将解码后的信息和整秒对应的时钟节拍(TICK)通过管理内存区共享给对时模块。对时模块负责守时,并将下一个整秒对应的TICK值和这一秒对应的TICK值通过管理内存区共享给FPGA,由FPGA完成对时报文组帧和发送。

另一方面,FPGA接收到串行通信报文后,使用直接内存访问(direct memory access,DMA)方式推送到循环报文缓冲区,更新管理内存区报文索引并通知其他模块处理。

主控模块硬件如图2所示。

图2 主控模块硬件框图

Fig.2 Hardware block diagram of the main control module

目前,串行通信总线较为常见的实现方式有控制器局域网(controller area network,CAN)和RS-485总线。本文高速串行通信总线采用RS-485。

主控模块通过串行通信总线与辅控模块进行通信。通信报文包括短周期的变量交换报文、长周期的对时报文,突发的调试下载报文等。短周期报文是实时报文,与主控模块任务周期相关。长周期报文和突发报文是非实时报文[7]。对时报文数据通信报文分时复用该通信总线,简化了系统硬件设计和布线成本,有利于现场施工和问题排查。

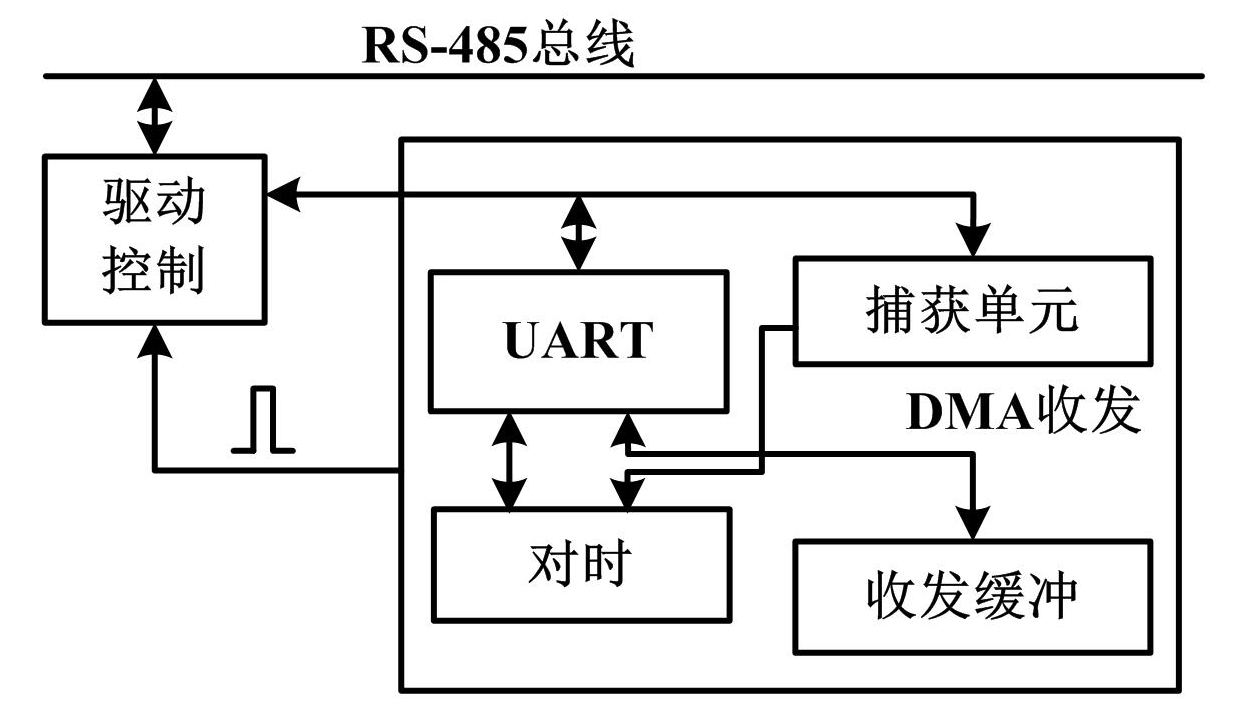

辅控模块硬件采用微控制单元(microcontroller unit,MCU)芯片原生通用异步收发器(universal asynchronous receiver/transmitter,UART)实现高速串行通信。系统设计DMA方式完成报文收发,从而有效地减少了MCU频繁收发报文的耗时[8]。

辅控模块MCU在UART接收超时中断中处理接收到的串口报文,在UART发送完成中断中进行RS-485收发方向控制,保证了收发控制的实时性。硬件上,MCU外部有RS-485总线驱动控制电路。这使得MCU必须周期性地向驱动控制电路发送脉冲才能发出报文,否则只能接收。软件上,MCU增加收发方向防误控制。当超过任务周期没有收到报文或者报文发送超时,则将收发方向强制为接收。这可以防止由于MCU软件跑飞或者收发方向控制失败导致高速串行总线挂死,增强了通信总线的健壮性。

辅控模块通过MCU自带捕获单元获取对时报文起始时刻。当MCU不具备捕获功能时,也可外扩FPGA处理高速串行通信报文并记录报文起始时刻。

辅控模块硬件如图3所示。

图3 辅控模块硬件框图

Fig.3 Hardware block diagram of the auxiliary control module

为了提高对时精度,主控模块串行通信模块由FPGA实现。虽然对时报文与数据通信分时复用同一总线,但由于主控模块发出的对时报文中包含发送起始时刻对应的精确时间戳,所以主控模块下发对时报文时刻不受整秒或者固定时间间隔限制。考虑到辅控模块的守时精度,主控模块下发广播对时报文的时间间隔一般在10 s以内。本系统中主控模块广播下发对时报文,将时钟同步功能集成于通信通道的空闲时隙中,每隔1 s左右下发一次。考虑辅控模块守时进秒机制,下发对时报文时刻一般在该秒的100~900 ms之间。

辅控模块接收主控模块下发的对时报文,并记录接收报文时刻对应的辅控模块内部时钟。由于辅控模块采用硬件捕获报文起始时刻,故捕获时刻不受关中断等程序执行的影响。

该报文时间戳信息,除串行通信模块发出报文起始时刻对应协调世界时(coordinated universal time,UTC)秒外,还包含发出报文时刻的纳秒时间,以及闰秒标志等。该报文中的纳秒时间是主控模块FPGA在对时报文发出时实时打上的时间戳,用于减少发送处理产生的误差。

主控模块下发的对时报文帧格式如图4所示。

图4 对时报文帧格式

Fig.4 Frame format of the time synchronization message

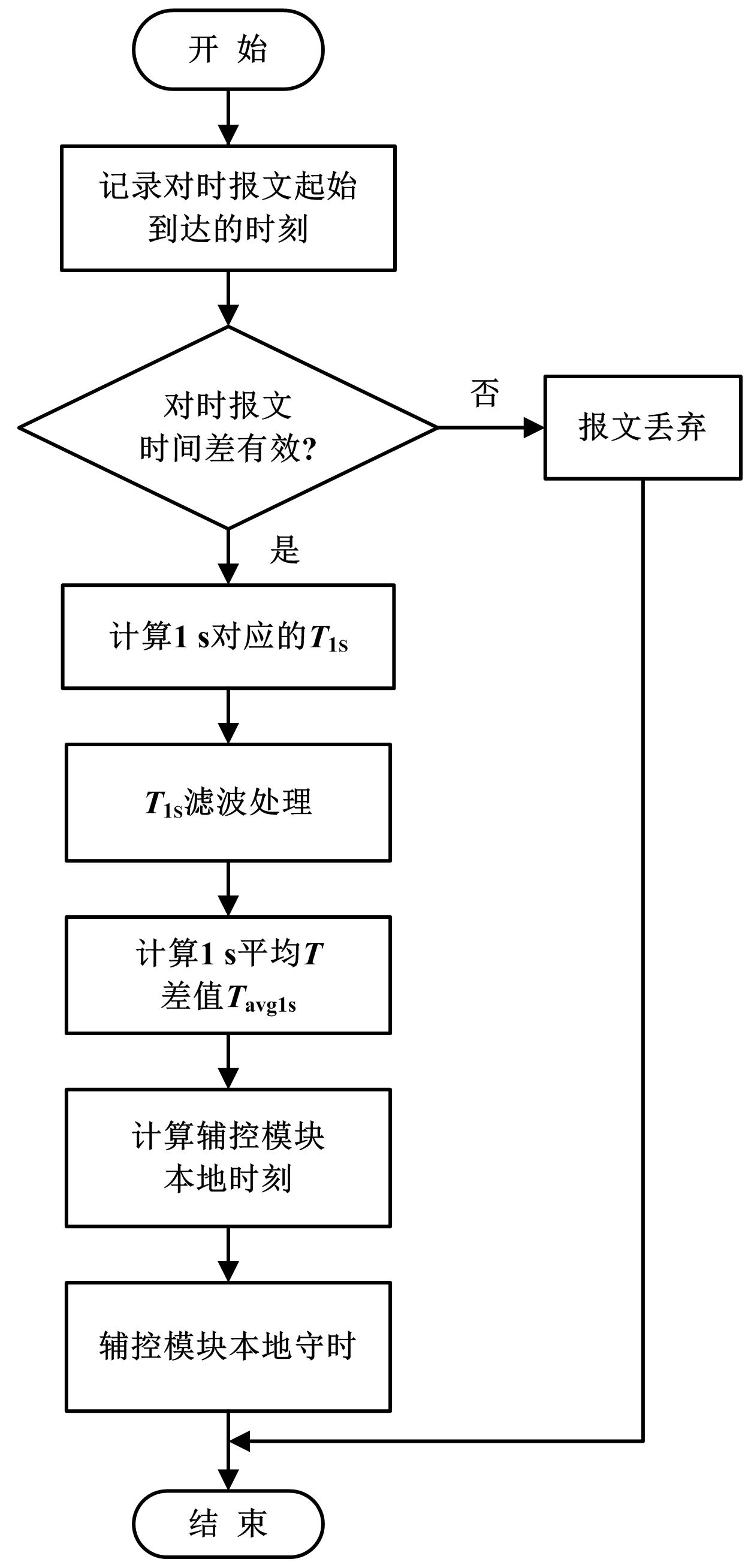

辅控模块接收对时报文处理流程如图5所示。

图5 对时报文处理流程图

Fig.5 Process flow of time synchronization message

辅控模块接收对时报文并记录报文起始到达时刻,并对接收报文的时刻的有效性进行校验。有效性校验包含绝对偏差和相对偏差两部分校验。绝对偏差是相邻2个对时报文携带时间戳的时间差与辅控模块内部节拍对应的时间差;相对偏差是2个对时报文的时间差归算到1 s后,与历史记录的偏差。当绝对偏差超过一定范围时,认为时钟发生跳变或受到干扰,偏差范围取主控模块和辅控模块晶振偏差之和,本系统取100 μs。当相对偏差超过一定范围时,认为时钟受到干扰,本系统取5 μs。当对时报文受到干扰时,该对时报文将被丢弃;当发生时钟跳变时,对时报文进行3次有效性确认。

根据相邻2帧报文中时间戳差值和辅控模块记录的TICK差值,计算1 s对应辅控模块的TICK差值T1s。其中,TICK即辅控模块系统时钟节拍。考虑到晶振抖动和上升沿捕获等误差,根据历史记录T1s,采用卡尔曼滤波算法计算出平均Tavg1s值[9-10]。结合主控模块下发时刻、辅控模块接收时刻和传输延时,即可计算辅控模块本地时刻。辅控模块在定时中断中对本地时钟进行维护,进入中断时读取当前TICK值,再根据Tavg1s对TICK差值进行修正,获取每次进中断的绝对时刻,从而进行守时管理。

串行通信网络一般没有转发环节,报文发送传输延时可以根据理论值推算。由于通信线长度改变造成传输延时的影响在几个纳秒级别,可以忽略不计。

当具有转发环节时,可以根据以下方法获取报文传输延时。主控模块向辅控模块发送报文包含时间戳T1。辅控模块接收到报文的时间戳为T2。辅控模块回复报文的时间戳为T3。主控模块收到回复报文的时间戳为T4。则报文发送传输延时d为[11]:

![]()

(1)

本文主要分析图1中没有转发环节的串行通信网络。为了提高系统对时的精确度和可靠度,辅控模块需要补偿报文发送传输延时和晶振偏差引起的时间差。辅控模块根据主控模块对时报文时间戳、报文发送传输延时和晶振偏差,推算辅控模块与主控模块时钟源的精确时间差,进而推算本地精确时间[12]。具体步骤如下。

①主控模块FPGA发出广播对时报文的时刻为S0、S1,...,Sn。辅控模块接收对时报文对应的辅控模块内部节拍依次为I0,I1,...,In。设辅控模块内部时钟源晶振理论频率为FS、实际内部时钟源晶振频率为FI,则辅控模块内部节拍到实际时钟的转换系数k为:

![]()

(2)

式中:n=1,2,...,N。

②使用相邻2次对时报文计算k值,会出现一定抖动。因此,本文采用上文提及的滤波算法进行计算。

③采用辅控模块理论晶振频率时,时间上距离辅控模块接收时刻In一定的时间间隔t。由于晶振偏差,对应实际时间间隔为:

t′=k×t

(3)

④若不考虑报文发送传输延时d,则对于主控模块当前时刻S,对应辅控模块的当前节拍I。则辅控模块的时刻为:

(4)

若考虑报文发送传输延时d,则对于主控模块当前时刻S,对应辅控模块的当前节拍I,辅控模块的时刻为:

(5)

结合上述过程,本系统产生误差主要在于以下几个方面。

①主控模块发送对时报文时,报文中的纳秒精度,误差一般在百纳秒级别。该部分误差一方面由FPGA硬件逻辑电路延时引起,另一方面由FPGA时钟精度和时钟颗粒度决定。

②线路传输延时,由传输介质决定,对于本文所述分布式系统内一般在几个纳秒级别。

③辅控模块捕获报文误差,受捕获边沿的波形质量和MCU捕获时刻精度影响,一般在几十纳秒级别。

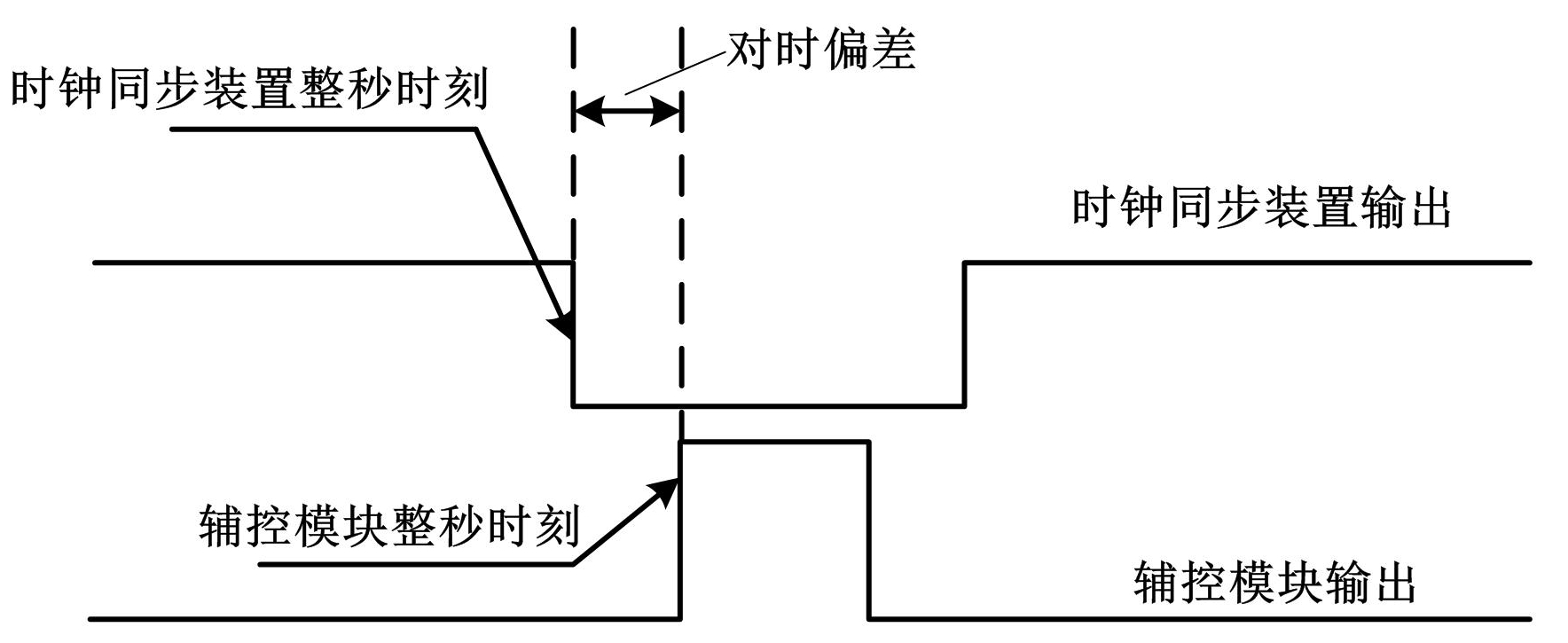

综合以上误差,采用该方案后,辅控模块的对时精度可以达到微秒级别。采用实际系统,在辅控模块中断检测整秒边沿并输出波形,与时钟同步装置秒脉冲输出对比,实测对时偏差在±2.5 μs以内。该测试包括中断响应引起的误差,已完全满足系统对时精度要求。

对时精度测试结果如图6所示。

图6 对时精度测试结果

Fig.6 Accuracy test results of time synchronization

本文介绍了一种基于串行通信的对时设计,将时钟同步功能集成于通信通道的空闲时隙中,布线方便、性能可靠。采用该对时设计的分布式系统已应用在光伏发电和电池管理领域,SOE精度经测试完全满足现场要求,在多个工程现场投入运行,得到良好的应用效果。

© 2024 All rights reserved. 北京转创国际管理咨询有限公司 备案号: 京ICP备19055770号-4

Transverture International Group Co Ltd, Guangdong Branch

地址:广州市天河区天河北路179号尚层国际1601

深圳市福田区深南中路2066号华能大厦

佛山顺德区北滘工业大道云创空间

东莞市大朗镇富丽东路226号松湖世家

梅州市丰顺县留隍镇新兴路881号

长沙市芙蓉区韶山北路139号文化大厦

欢迎来到本网站,请问有什么可以帮您?

稍后再说 现在咨询